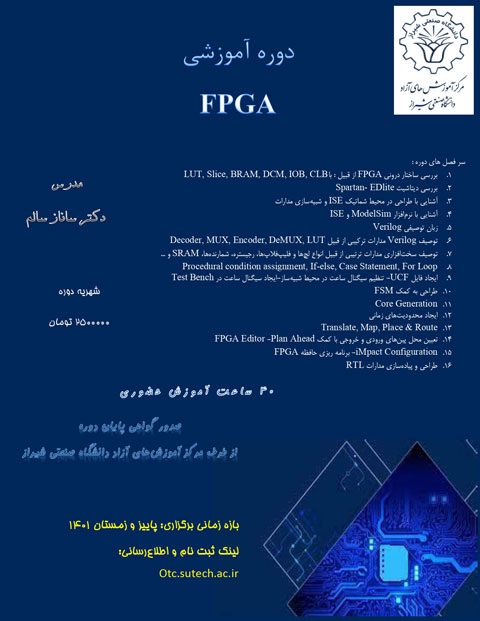

سرفصلها و مباحث دوره:

- بررسی ساختار درونی FPGA از قبیل CLB, IOB, DCM, BRAM, Slice, LUT

- بررسی دیتاشیت Spartan-EDlite

- آشنایی با طراحی در محیط شماتیک ISE و شبیهسازی مدارات

- آشنایی با نرمافزار ModelSim و ISE

- زبان توصیفی Verilog

- توصیف Verilog مدارات ترکیبی از قبلی Decoder, MUX, Encoder, DeMUX, LUT

- توصیف سختافزاری مدارات ترتیبی از قبیل انواع لچها و فیلپفلاپها، رجیستره، شمارندهها، SRAM و …

- Procedural Condition Assigment, If-Else, Case Statement, For Loop

- ایجاد فایل UCF – تنظیم سیگنال ساعت در محیط شبیهساز – ایجاد سیگنال ساعت در Test Bench

- طراحی به کمک FSM

- Core Generation

- ایجاد محدودیتهای زمانی

- Translate, map, Place & Route

- تعیین محل پینهای ورودی و خروجی با کمک FPGA Editor Plan Ahead

- iMpact Configuration – برنامهریزی حافظه FPGA

- طراحی و پیادهسازی مدارات RTP

شهریه: ۲ میلیون و ۵۰۰ هزار تومان

۴۰ ساعت آموزش حضوری همراه با گواهی پایان دوره از مرکز

مدرس و مسئول برگزاری این دوره، خانم دکتر سالم است. فراگیران محترم درصورت داشتن سوال در مورد این دوره میتوانند با شماره تلفن مرکز (37353101) بگیرند.